# Controlling ESD Damage of ICs at Various Steps of Back-End Process

# John Marley (1), David Tan (2), Vladimir Kraz (3)

- (1) Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 Tel. 408-879-6104 e-mail John.Marley@xilinx.com

- (2) Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 Tel. 408-879-6457 e-mail David.Tan@xilinx.com

- (3) Credence Technologies, Inc. 3601-A Caldwell Dr. Soquel, CA 95073 Tel. 831-459-7488 e-mail vladimir@credencetech.com

Abstract: In this work we study the methodology of ESD Event identification and their correlation with operation of equipment at various stages of the back end IC manufacturing. Survey of ESD environment in terms of exposure of ICs to known strength of ESD Events is described. Such correlation is instrumental in identification of sources of ESD damage and in setting up and maintaining ESD-safe environment.

## I. Introduction

The ESD issues at the back end of the IC manufacturing have resurfaced in the past few years mostly due to the following factors:

- Smaller geometry means higher sensitivity to ESD. It takes much less energy to destroy a trace or a device on a die of 0.13μ than of 0.35μ.

- Conventional ESD protection measures are not fully compatible with high-speed signals. Their relatively high parasitic capacitance substantially affect slew rate and rise and fall time of pulses at high speed. Smaller-capacitance protective devices affect high-speed signals to a lesser degree, however they offer much less protection against ESD. RF/MMIC ICs cannot afford to have the level of ESD protection that is common for digital ICs.

- Increased number of I/O pins statistically increases probability of IC failure

- Larger die sizes make losses more expensive

- ICs exposed to ESD may not fail right away latent damage causes losses and alienates customers

- Increasing cost pressure demands reduced handling time. The result: ICs move faster. Conventional ESD protection measures (i.e. ionizers, etc.) cannot handle such rapid movement. It takes several seconds for an

ionizer to discharge IC to a safe voltage level. In these few seconds several ICs, for example, will be tested and moved away from the test area. It is often not possible to increase discharge rate by increasing airflow from ionizers because flow of air cools down the ICs that are supposed to be tested at controlled elevated temperature. The result is more frequent ESD Events resulting in ESD damage to the ICs.

Contact Infotmation:

vkraz@bestesd.com

www.bestesd.com +1-408-202-9454

Vladimir Kraz

# II. Purpose

This paper deals mostly with methodology of identifying ESD Events and measuring their strength in actual production environment. Methodology, tools and procedures are described with the purpose of helping to apply verification-based ESD program to IC manufacturing. Special effort was made during the experiments leading to this paper to isolate each ESD Event to a specific step in the process since this is the only fact-based way to minimize ESD exposure.

This way specific actions can be taken in order to alleviate the problem and eliminate guesswork. Specific solutions to reduce ESD Event occurrences in tools and workstations are often more productive and more cost effective than blanket ESD program with no indication of success.

It is also helpful to know whether an IC is ever exposed in the process to ESD Events higher than

the determined damage threshold level. If an IC is found to have been exposed to ESD Event above determined threshold, it can be subject to latent damage.

# III. Methodology and Tools

For monitoring and measuring ESD Events we used EM Aware ESD Event monitors manufactured by Credence Technologies that measure electromagnetic emission generated by ESD Events and present each event in a form of a pulse whose magnitude is a function of energy of the discharge. Figure 1 shows typical output of ESD Event monitor.

Figure 1. Typical Response of ESD Event Monitor. Each Pulse Represents ESD Event and its Magnitude.

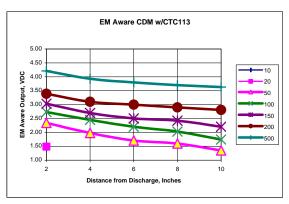

The response of ESD Event monitor is a function of a distance from the source of discharge due to nature of propagation of electromagnetic waves. Figure 2 shows typical response of EM Aware to CDM-type discharges based on their strength and distance from the source. Characterization data for EM Aware were used to access the strength of each individual ESD Event and to set the

Figure 2. EM Aware Characterization Data for CDM Discharge

threshold below which weak ESD Events are ignored.

Remote antenna of ESD Event monitors was positioned as close as it was practical to the anticipated source of ESD Event for better identification of ESD Event sources.

In each case wherever possible an antenna of ESD Event monitor was placed at known distance from point of contact to pins of IC as close to possible site of discharge as it was practical.

The effort was extended to identify every ESD Event with specific action of the tool and step of the process.

# IV. Specific Areas of ESD Damage

# IV.a. IC Testing

Several specific steps in the process of IC testing where ESD Events occur were observed:

- when the IC is being placed on the test pad

- when the IC is being removed from the test pad

- when the IC is being placed in the exit shuttle (tray).

In two latter occurrences the IC was exposed to dangerous levels of ESD *after* it has been tested. The problems associated with it are that

- possibly defective IC can be shipped to a customer

- there is no feedback mechanism to pinpoint the source of the failures that allows implementation of corrective actions.

This agrees with findings of [1] and [2].

There are several reasons for ESD Events occurring at each described step. Some of them are not obvious on the surface, however they agree with physics of generation of static charge.

When IC is lifted by a vacuum picker from the input shuttle (tray) the charge is often generated. Though the material of the tray may be static-dissipative, this doesn't guarantee that charge is not generated when the IC pins and body are separated from the tray.

Even if material of some trays is labeled as "static-dissipative," many such materials are dissipative only laterally and are insulative across layers, offering little or no dissipation from ICs to grounded metal surface on which the tray is positioned. That means that ICs and a tray may be containing charge when the tray arrives.

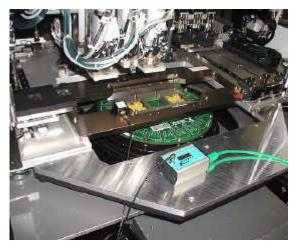

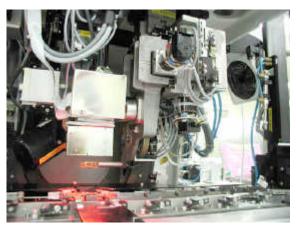

Figure 3. Placement of Antenna Near the Test Pad in the IC Tester

When the robotic arm moves in the IC tester, its grounding is in question since it is often done via ball bearings on which that arm is mounted to the frame. Ball bearing offers intermittent contact to the ground since it is comprised of metal parts separated by insulative lubricant. Due to rapid movements of the robotic arm, it may get

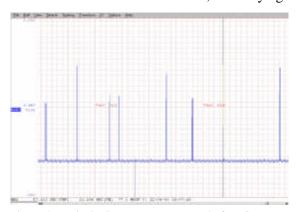

Figure 4. Typical ESD Events at Test Pad of at IC Tester

charged extremely quickly and this charge is easily transferable to the IC in a process of being moved.

When IC is lifted from the test pad, a charge is often generated. When IC is rapidly lifted, the voltage between the IC and the pad increases

accordingly to the reduction of capacitance between the two in agreement with the basic formula:

$$Q = C*V$$

On occasion, this voltage is enough to break the air gap and produce a discharge between pins of IC and grounded metal parts.

During investigation, remote miniature sensors of ESD Event monitors were positioned next to each possible point of contact in order to identify the sources of discharge. ESD Events were closely identified with each movement of ICs and equipment.

On the IC tester, the remote antennae of the ESD Event monitors was placed in several different areas, specifically near the test pad, near the exit shuttle and near the input shuttle. This allowed identification of origin of each ESD Event by magnitude of the event captured. Typical position of the antenna next to the test pad is shown in Figure 3. The specific distance of antenna from the pad it this case was 3" (7.5cm).

Figure 4 shows experimental data collected at the test pad. As seen from the chart, observed ESD Events were as strong as 400V CDM.

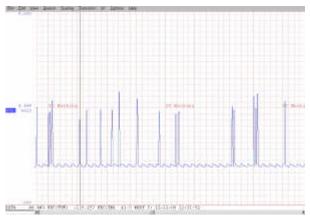

Figure 5 shows ESD Events at the exit shuttle.

Figure 5. Typical ESD Events at the Exit Shuttle. Note dual discharges (see text)

Please note "double hits." The first event was associated with the discharge on nearby test pad, the second one – discharge on the exit shuttle The time interval between the events is about 1 second – this what it takes for the IC to be lifted from the pad and placed into the shuttle. As it seen on the chart, some events in the shuttle are multiple (shown as several very closely-spaced

events). The maximum magnitude of observed event in this case was 230V CDM.

Several measures were taken in order to institute manageable ESD situation within the tester. These measures included installing appropriate ionizer with verified performance and setting it with the optimal air flow pattern, grounding rotating robotic arm with the flexible wire for positive ground contact, reviewing material of trays, etc.

An area of consideration is to connect output of ESD Event monitor to the handler itself, so that when a strong ESD Event above set threshold is observed, the IC can be channeled into a different bin for more thorough testing and/or as a suspect for latent damage.

#### IV.b. Die Attachment

The investigation pointed at a specific source of ESD Events in a die attachment process that was damaging dies. The specific instance of occurrence of ESD Event was associated with the die picker contacting the die in a tape package prior to moving this die to bonding. Typical die attachment setup is shown in Figure 6.

Figure 6. Typical Die-Attachment Setup

A die resting on a tape (seen in a background of Figure 6) already has charge. Ionizer was of little help because as seen, its position was not optimized and airflow is directed with the idea of providing ionization to the area of die attachment, not die separation from the tape. Ionizer is positioned too far away anyway to be effective in the area of die attach as well. When vacuum picker touches the die, a discharge occurs that could be harmful for the die. Strength

of discharges associated with this particular operation was observed up to 500V CDM.

Situation is aggravated by the fact that die gets charged when it is separated from the tape. Combination of rapid movement of robotic arm and insufficient ionization results in occasional discharge to the frame when die is placed on the frame even though the bottom of die is insulative.

## IV.c. Ball Bonding

Discharges were observed during ball attachment process. Miniature balls were charged when they were picked up and when they were released from vacuum carrier. Each ball carries little charge due to its small size (0.030" diameter), however the discharge to each terminal of the IC is focused and is targeted, so such discharge cannot be dismissed. Discharges of 50V CDM were observed during ball attach process. While for some ICs this level does not seem to be sufficient to cause problems, it may be problematic for newer generation of ICs and be instrumental in generating latent damage defects.

# IV.d. IC Marking

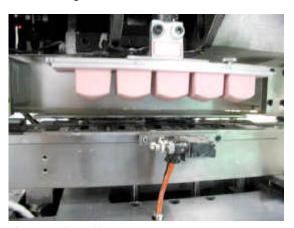

The IC marking process is capable of generating substantial ESD Events. A typical marker is shown in Figure 7.

Figure 7. IC Marking

Insulated pads get highly charged by tribocharging without much possibility of discharge due to their fast movement and the fact that flow of air from ionizer may dry ink. These pads transfer their charge to the ICs via induction and also create new charge via tribocharge when separating from the IC package. Discharges were observed when pads touched the ICs and when

they were separating from them. Both automated and manual marking operations exhibited high level of ESD activity.

It is important to notice that charge by induction can occur not only to the ICs but also to moving metal parts of the tool that do not have positive connection to ground at all times. Such metal parts are capable of producing strong discharges to either other metal parts or to IC terminals

Figure 8. Discharges During IC Marking Process

making ESD environment at the station uncontrollable unless all metal parts are positively grounded at all times. Flexible wires can be successfully used to ground all moving metal parts.

Multiple discharges are frequent at this stage, partially because several ICs get marked at once. Discharge strength can reach as high as equivalent of 500V CDM but often is kept at approximately 120V CDM level.

Figure 8 shows typical discharge data at IC marking process.

#### **IV.e.** Other Operations

Observed but not covered in this paper processi include lead trim, lead form, lead scan, final visual inspection and other.

### V. Conclusion

Fact-based ESD management allows focused attention to real ESD problems in IC manufacturing. Real-time monitoring and measurement of ESD Events is instrumental is identifying specific steps of the process where ESD damage occurs, assess the magnitude of exposure, implement corrective actions and

verify their effectiveness. Monitoring of ESD Events allows certifying of tools that they do not expose ICs to ESD Events higher than allowed limits. It is therefore feasible to assure that no IC that has been exposed to harmful ESD Event is shipped to the customer and the customer can be provided with the record of ESD exposure to his products at every step of the process.

Further recommendation may include marking ICs that were exposed to high levels of ESD as subjects for latent damage.

## VI. References:

- [1] Way Kuo (Fellow, IEEE), and Taeho Kim, "An Overview of Manufacturing Yield and Reliability Modeling for Semiconductor Products. Proceedings of the IEEE August, 1999 Volume 87 Number 8."

- [2] Joe Bernier, Bruce Hesher, Harris Semiconductor (now Intersil), Melbourne. Florida. USA. "ESD Considerations Semiconductor Back-End Manufacturing Operations"

- [3] R. G. Wagner, J. M. Soden, and C. F. Hawkins, "Extent and Cost of EOS/ESD Damage in an IC Manufacturing Process", (EOS/ESD) Symposium Proceedings, pp. 49-55, Sept. 1993.

- [4] V. Lakshminarayanan, "Design Techniques to Control Electrostatic Discharge Damage in Electronic Devices" Integrates Systems Design Magazine, 4/2000.